### ELECTRONICS

VOLUME 14 No. 13 SEPTEMBER 1978

CONSTRUCTIONAL PROJECTS

### ANALOGUE COMPUTER-1 by P. J. Kronis BSc. Mathematical operations and circuits 970 COMBINATION LOCK by E. A. Parr Double combination for added security 990 THERMOSTAT CONTROL by M. Edmunds For the photographer who does his own developing 1002 SOUND TRACK MONITOR by J. Schmid Alerts the operator when the end of a recording is reached 1006 METRONOME by M. Butt Simple emphasised beat unit 1010 KEYBOARD by L. G. Parkin BA Provide an eight bit binary word by pressing two keys 1014 **GENERAL FEATURES** WAVE ENERGY by M. Abbott Can the sea provide the UK with electricity? 976 STRICTLY INSTRUMENTAL by K. Lenton-Smith Signetics TDA 1008 electronic music i.c. 988 **INGENUITY UNLIMITED** Simple Clock—Beethoven's Doorbell—Electronic Combination Lock—Distortion Assessment—Protection for a Model Train Speed Controller—Simple Alarm 993 SEMICONDUCTOR UPDATE by R. W. Coles A look at some recently released devices 998 **NEWS AND COMMENT** EDITORIAL 969 READOUT A selection of readers letters 974 **BOOK REVIEWS**

Our October issue will be on sale Friday, 8 September 1978 (for details of contents see page 975)

Soyus-29 and Salyut-6, USSR Launchings, India and the USSR, GOES-3, Place in Space

© IPC Magazines Limited 1978. Copyright in all drawings, photographs and articles published in PRACTICAL ELECTRONICS is fully protected, and reproduction or imitations in whole or part are expressly forbidden. All reasonable precautions are taken by PRACTICAL ELECTRONICS to ensure that the advice and data given to readers are reliable. We cannot, however, guarantee it, and we cannot accept legal responsibility for it. Prices quoted are those current as we go to press.

Selected new books we have received

INDUSTRY NOTEBOOK by Nexus What's happening inside industry

SPACEWATCH by Frank W. Hyde

Thought provoking ideas on file at the British Patents Office

MARKET PLACE Interesting new products

**PATENTS REVIEW**

980, 1013

985

1001

1005

1020

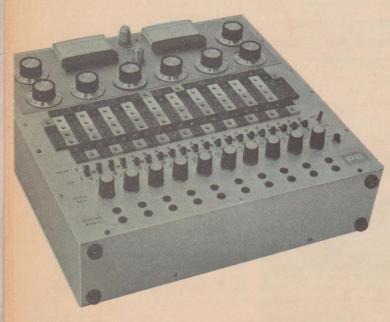

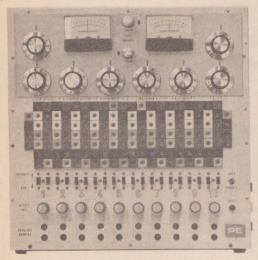

- \* Ten Amplifiers

- ★ Eight Coefficient Multipliers

- Two Four Quadrant Multipliers

- Over Voltage Indicators on all Amplifiers

- ★ Provision for "Initial Conditions"

- ★ Offset Null on all Amplifiers

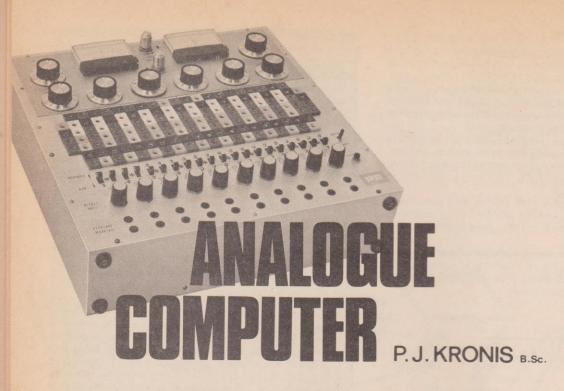

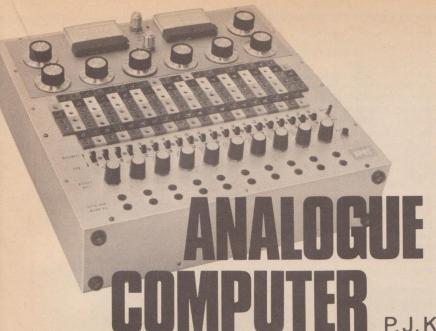

## ANALOGUE COMPUTER

P.J. KRONIS B.Sc.

PART 1

THE analogue computer is a piece of equipment designed to satisfy mathematical equations, usually differential. Mathematics in general and differential equations in particular are the subjects of an exact science which describes the behaviour of physical systems.

Because computers cannot tell us how to solve a physical problem a mathematical model of the problem has first to be formed by the programmer. This is where computers are useful because the formation of the mathematical model is usually easier than the solution of the equations especially as differential equations can be particularly difficult to solve manually and some virtually impossible.

The analogue computer works by handling continuously changing variables using electrical potential or voltage as the analogue, in contrast to the digital computer which manipulates discrete pulses to obtain the solution to a problem.

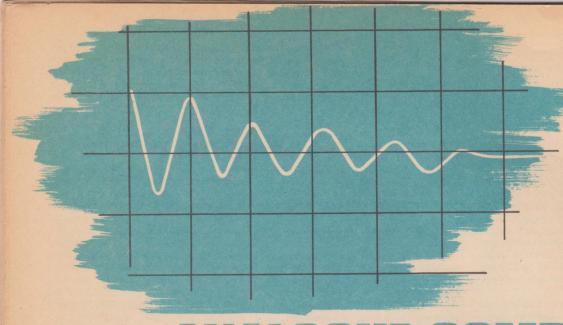

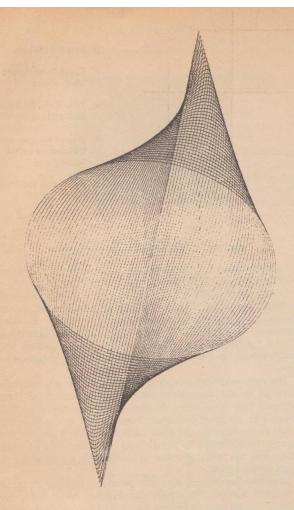

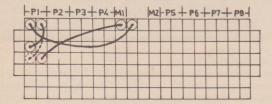

Fig. 1.1 was produced by the analogue computer to be described here and it will be explained in this article how to program the computer to produce these interesting and artistic designs.

The analogue computer can be used in engineering to simulate the behaviour of complex systems before they are constructed, the behaviour of these complex systems can be thoroughly studied and various parameters changed simply by turning a potentiometer until the system functions in a satisfactory manner. This procedure allows considerable savings both in the cost and time of development.

Analogue circuits similar to those used in analogue computers are employed in a variety of applications, i.e. automatic control in industry, aircraft and spacecraft.

One of the examples to be given in this article will be a simple program to simulate the vertical take-off of an aircraft like the Harrier jump jet, and also a spacecraft moonlanding.

### **MATHEMATICAL OPERATIONS AND CIRCUITS**

The advances in miniaturisation have enabled more computing power to be packed into a smaller space and it is these advances that have helped the digital computer on its way towards becoming a household object. In the analogue

Fig. 1.1. A typical lissajous figure produced using the Analogue Computer and an X-Y plotter

field the high gain d.c. amplifier or operational amplifier which is the main element of the analogue computer, has also come a long way since its inception. It was originally designed for use in computers but has since found many applications in other fields. This large market for other applications has reduced the cost of such devices to very low levels. Of the numerous op-amp i.c.s available on the market the 741 was chosen for the prototype because it is both cheap and easy to handle. More advanced op-amps are available albeit at a higher price and constructors can experiment with these if they wish.

By connecting an op-amp to input and feedback components certain mathematical operations can be performed; addition (and subtraction) integration, and multiplication by a constant. Differentiation can also be performed but is generally avoided due to problems associated with noise generated by components. Multiplication by constant coefficients between zero and one is also performed using potentiometers with some special circuits being employed to enable the multiplication of two variable voltages.

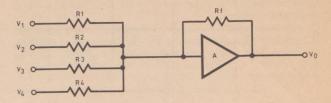

### THE ADDITION CIRCUIT

It is possible to add various voltages by means of a resistance network with the output voltage being proportional to the sum of the input voltages. The serious drawback of this method is that this is only true if the load resistance remains constant.

This would be an unacceptable constraint since the output voltage may be applied to other points in the circuit which have different values of load resistance.

To overcome this difficulty a high gain d.c. amplifier is employed in the feedback circuit as shown in Fig. 1.2.

Fig. 1.2. "Addition" circuit

If a voltage  $V_1$  is applied via  $R_1$  to the summing junction the output voltage  $V_0$  is equal to

$$-V_1 \frac{Rf}{R_1}$$

The polarity of the input voltage is also changed by the operational amplifier.

With the output voltage now independent of the load resistance each input voltage is factored by the same ratio of feedback resistance to input resistance.

$$V_{o} = -\left(V_{1} \frac{Rf}{R_{1}} + V_{2} \frac{Rf}{R_{2}} + V_{3} \frac{Rf}{R_{3}} + V_{4} \frac{Rf}{R_{4}}\right)$$

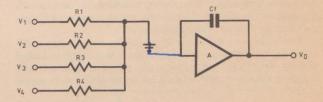

### THE INTEGRATOR CIRCUIT

As with the addition circuit integration can be achieved by using an R.C. network but this method also suffers from a number of serious drawbacks.

The circuit in Fig. 1.3 shows how an operational amplifier can be used to perform integration.

Fig. 1.3. "Integrator" circuit

With a capacitor connected in the feedback loop, and if the open loop gain of the amplifier is very large, the output voltage is given by

$$V_{o} = -\left(\frac{1}{R_{1}Cf}\int V_{1}dt + \frac{1}{R_{2}Cf}\int V_{2}dt + \frac{1}{R_{3}Cf}\int V_{3}dt + \frac{1}{R_{4}Cf}\int V_{4}dt\right)$$

The output voltage is the sum of the integrals, with respect to the time the voltage is applied to the inputs,

factored by

$$-\frac{1}{Rin}$$

Cf.

By choosing suitable values of Rin and Cf the factors can be given the required values.

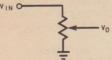

### THE COEFFICIENT MULTIPLIER

The coefficient multiplier is used to multiply a voltage by a constant between zero and one. This is the only mathematical operation that is usually performed without the use of an op-amp. A potentiometer is connected as shown in Fig. 1.4.

At one extreme of the slider's travel Vo=Vin, i.e. Vin is multipled by 1, whereas at the other extreme Vo=0 i.e. Vin is multiplied by zero.

Any intermediate value can be set up by moving the slider. The dial of the potentiometer can be calibrated to facilitate this. However, it is not normal practice to set up a value on

Fig. 1.4. Coefficient Multiplier

the dial of the potentiometer because this circuit also suffers from the effects of load resistance.

An op-amp employed as a voltage follower could be connected as a buffer to isolate the effects of the load resistance, but this is an unnecessary addition because the problem can be overcome by measuring the output of the potentiometer using a voltmeter, after the circuit has been connected, i.e. in the presence of the real load to be applied in the particular problem being examined. The value desired is then set by adjusting the potentiometer and ignoring the graduations on the dial.

The circuits described so far form the fundamental building blocks of the analogue computer. Various special circuits have been developed over the years for other operations. The most important of which is the formation of the product of two variables. One of the early methods developed was the cumbersome servo multiplier. This involved the control of potentiometers using servos. Nowadays this operation can be achieved electronically using four-quadrant multiplier integrated circuits.

### INTEGRATION

Addition, subtraction and multiplication are concepts that are easily understood; integration, however, is not so easily grasped by the non-mathematically minded and so a simple explanation may be useful at this point.

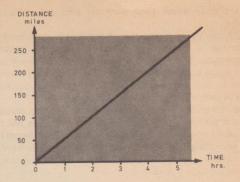

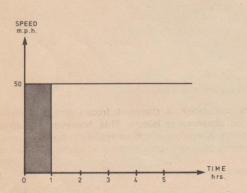

If for example a motor car is cruising on a motorway at 50 miles per hour this can be represented by a graph of speed against time (Fig. 1.5). Since the speed is constant the distance travelled will increase by equal amounts in equal

Fig. 1.6. Graph of distance against time

time intervals. These distances are shown plotted on a graph of distance against time for intervals of one hour (Fig. 1.6).

It can be seen from Fig. 1.5 that the distance travelled during a period of time is represented by the area shown shaded on the velocity-time graph. (Velocity × time representing the height × base of the shaded rectangle.) Now if the results of all these intervals were added up, the result would be the total distance travelled in a period of time.

The mathematical way of saying this is that the distance travelled is the integral of velocity with respect to time between two time limits. In the above example since the speed was constant one could have arrived at the required result by multiplying the total period of 5 hours say, by the velocity of 50 m.p.h. to obtain 250 miles travelled, without going into the trivial process of integrating, by considering small time intervals.

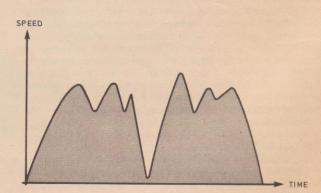

In reality the velocity may vary as shown in Fig. 1.7, i.e. in a random manner. To obtain the required result then, the velocity would have to be integrated over the required period of time by considering small time intervals. This is how a digital computer would be programmed to solve the problem. The accuracy in that case would depend on how small the time intervals were made. This is left to the discretion of the programmer. If the intervals were made too big, then the result would be inaccurate. On the other hand too small a time interval would mean that the computer would take longer to solve the problem and involve the programmer in unnecessary expense. The analogue computer programmer need not worry about this since the computer integrates continuously, i.e. it deals with

Fig. 1.5. Graph of speed against time

Fig. 1.7. Graph showing variations in velocity

infinitesimally small time intervals and does this at high speed.

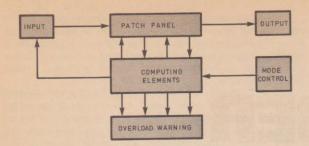

Each of the circuits that have been described so far constitutes a computing element. When the computer is programmed to solve a problem, systems of equations can be set up by connecting together combinations of computing elements, and the results can be obtained by measurements taken at various points in the system.

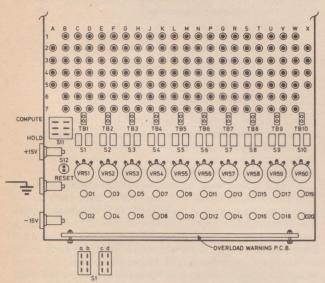

The computer will of course be required to solve many different problems and the computing elements will have to be rewired every time. To facilitate this a patch panel is used, with sockets connected to each computing element in the computer. By using wire leads the computing elements can be connected in any order.

INTEGRATOR

At the beginning of a computation the variables of the problem will have certain values, not all of which need be zero. The requirement here is that is should be possible, if desired, to give the output of integrators a value, before the computation commences. This facility is called "Initial Conditions".

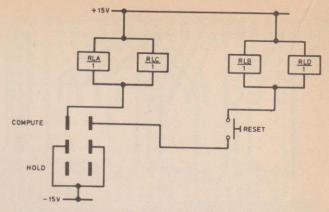

Fig. 1.7 shows how the "Initial Conditions" for the "Compute", "Hold" and "Reset" facilities are achieved for summers and integrators. In the case of the summers no change in the circuit is necessary. For the integrators, the "Hold" mode requires that the input resistors are disconnected from the op-amp and grounded. In this way the charging or discharging of the capacitor stops and the op-amp maintains the charge at a constant level.

SUMMER

#

Fig. 1.8. "Initial Condition" circuits for Integrators and Summers

### **MODE CONTROL AND INITIAL CONDITIONS**

The main modes of operation are compute, hold and reset. When in the compute mode the computer proceeds to solve the problem. As it is sometimes desirable to stop the computation after a certain period of time this is achieved by putting the computer into the "Hold" mode. The "Reset" mode is used to make the output of all computing elements take their initial value. Sometimes this mode is called "problem check".

"Reset"

The calculation is therefore frozen and the results can then be observed at leisure. This, however, should not be practised literally, since electronic components, like everything else, are not perfect and some drift will always affect the results. These should therefore be noted as soon as the "Hold" mode has been selected.

"Reset"

The "Reset" mode for the integrators has two resistors  $R_{ic}$  in the circuit. These are the "Initial Conditions" resistors and when an initial condition voltage,  $V_{ic}$  is applied as shown, the

Fig. 1.9. Block diagram of the Analogue Computer

feedback capacitor charges up to this value. When "Compute" is selected these resistors are disconnected and the output of the amplifier, i.e. the voltage across the feedback capacitor, may vary above or below the initial condition value. When "Reset" is reselected the feedback capacitor discharges or charges, through  $R_{\rm i_{\rm c}}$  to  $V_{\rm i_{\rm c}}$  and the computer is again ready for a repeat of the calculation.

### THE OVERLOAD WARNING FACILITY

This facility, usually employed in analogue computers, is necessary because the voltage range over which operational amplifiers operate linearly, is limited to approximately ±13V for readily available i.c.s. In the course of the solution of a problem, all computing elements must operate within this range, otherwise the wrong results will be obtained. The overload warning circuit warns the programmer of any amplifiers that have saturated. Measures can then be taken to scale down the values of the variables.

It is now possible to imagine the general arrangement of an analogue computer and this is depicted by Fig. 1.9 in a block diagram form.

To summarise, input signals are fed to the computing elements via the patch panel and are processed. The results are fed back through the patch panel to the output, which may be an ordinary voltmeter, a CRO or an X-Y recorder. The operation of the computing elements is controlled by the Mode Control and the overload warning circuit monitors the output of the computing amplifiers and warns the programmer of any saturating amplifiers.

**NEXT MONTH: CONSTRUCTION DETAILS**

## readout

### ... a selection from our postbag

Readers requiring a reply to any letter must include a stamped addressed envelope.

Opinions expressed in Readout are not necessarily endorsed by the publishers of Practical Electronics.

### **Champ Waves**

Sir—I hope you can clear up the confusion that has arisen about your EPROM programmer in the CHAMP series.

When purchasing INTEL 1702A EPROMS I was sent a data sheet, which detailed the programming voltages as completely different from those produced by CHAMP-PROG. Since you said that INTEL had supplied the basic circuit for your project, and use it in their "Intellec" development systems, it has resulted in much head scratching on my part.

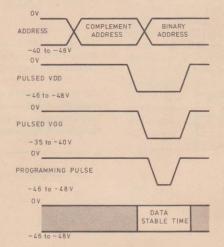

The waveforms given on the data sheet are as shown.

Any clarification you can give will be greatly appreciated.

T. G. Keslake Romford Essex

I can understand your confusion over the difference between the 1702A data sheet and the operation of the CHAMP-PROG board, but really it is quite simple. You will notice in the data sheet that all voltages are related to GND or 0 Volts, and this means that all chip voltages are related to the Vcc pins. In CHAMP-PROG the voltages appear to be positive going, but if you look at the Vcc reference pins you will find that they rise to +47V during programming, and this means

that the program pulse is a 3ms -47V pulse as required. As with many things in electronics, the secret lies in viewing the circuit operation with one's feet firmly on the ground (or in this case, the ceiling!). If you check the other supplies with this new perspective, you will find that they are substantially as dictated in the data sheet.

Once again, I quite understand your initial confusion!

R. W. COLES

### Too Powerful

Sir,—Working as Product Marketing Engineer for the UK's largest distributor of National Semiconductor products I was highly amused by the letter which appeared in the July issue of P.E. from reader R. G. Silson.

I can only assume from reading his letter that he must be extremely well versed in the world of microprocessors—indeed he must know far more than the vast majority of industry's electronics engineers.

Dealing with engineers every day from all fields of the electronics world I quite naturally get a very good indication of their thoughts and feelings towards various projects.

The number of times I have spoken to customers about the Pace microprocessor, only to be told "Not interested—it's too powerful for what we need", is more than ample evidence for myself that Mr Silson is completely out of touch with the amount of knowledge possessed by the average amateur actively engaged in microprocessors. Further proof of this is the vast amount of 8 bit SC/MP chips sold related to the relatively slow moving Pace.

P. V. Hodson, Melton Mowbray, Leicestershire. PRACTICAL

### ELECTRONICS

OCTOBER 1978

45p

### ELECTRONICS

VOLUME 14 No. 14 OCTOBER 1978

### CONSTRUCTIONAL PROJECTS P.E. V.D.U. SYSTEM—1 by A. A. Berk, B.Sc., Ph.D. Up to date "one chip" memory mapped system 1054 FUEL CONSUMPTION METER By J. McCarthy An aid to economy, suitable for most cars 1060 HIGH PERFORMANCE POWER SUPPLY UNIT by R. Lawrence, B.Sc. Voltage control down to zero, plus current limiting 1070 ANALOGUE COMPUTER—2 by P. J. Kronis, B.Sc. 1074 Construction details TWO RANGE TIMER by J. D. Jardine A portable, inexpensive general purpose unit 1088 **GENERAL FEATURES** IMPEDANCE by Toby Bailey and Bob Whitaker 1066 Do you understand it? MICROBUS by D.J.D. 1098 A bi-monthly focus on micro's for the home constructor INGENUITY UNLIMITED Capacitor Continuity Tester—Synthesiser Repetitive Waveform Generator Simple Fuzz—Accenting Metronome—Stereo Indicator 1080 **External Input Unit for Synthesisers NEWS AND COMMENT** 1049 **EDITORIAL** MARKET PLACE 1050 New products SPACEWATCH by Frank W. Hyde 1053 Pluto, More from the USSR, Copernicus discovers Black Hole **POINTS ARISING** 1058 Linear Capacitance Meter, Dimwit, Kiln Controller 1084 **BOOK REVIEWS NEWS BRIEFS** Strain Gauge—Big Brother Check—Micro Power Pack—Computers Galore Club 1087 Underground Cameras—Steam Advice—Here's To Progress 1090 1094 **Teletext Course** Disc Full of Holes 1102 **HOW TO USE YOUR FREE STICKIES** 1093 **INDUSTRY NOTEBOOK** by Nexus 1097 What's happening inside industry **PATENTS REVIEW** 1100 Thought provoking ideas on file at the British Patents Office READOUT 1102 A selection of readers' letters

Our November issue will be on sale Friday, 13 October 1978, price 50p (for details of contents see page 1059)

© IPC Magazines Limited 1978. Copyright in all drawings, photographs and articles published in PRACTICAL ELECTRONICS is fully protected, and reproduction or imitations in whole or part are expressly forbidden. All reasonable precautions are taken by PRACTICAL ELECTRONICS to ensure that the advice and data given to readers are reliable. We cannot, however, guarantee it, and we cannot accept legal responsibility for it. Prices quoted are those current as we go to press.

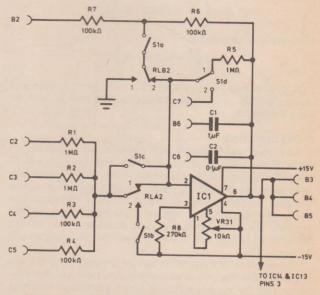

PART 2

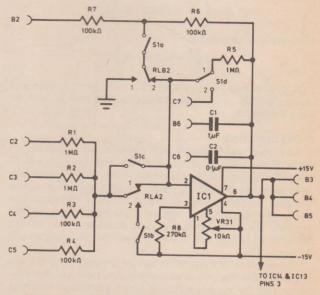

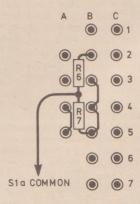

AVING formed a general picture of the workings of the analogue computer, the complete circuit of a computing element can now be described. This is shown in Fig. 2.1. The basic circuits of input and feedback, components connected around the op-amp can be readily recognised. The input comprises four resistors, R<sub>1</sub> to R<sub>4</sub>, which are connected to sockets in the patch panel and to the inverting input of the op-amp, via switches RLA2, S1c, and S1b. The feedback circuit consists of R5, C1 and C2, which can be selected by means of switch S1a and sockets (C7, B6 and C6) on the patch panel.

Consider switch S1a set so that R5 is selected in the feedback loop. The computing element now becomes a summer. By recalling the equation for the addition circuit that was described last month and by substituting the values for R5, R1, R2, R3, and R4 it can be seen that a voltage applied at inputs 1 and 2 will be multiplied by unity,

$$\left(\frac{R5}{R1 \text{ or } R2}\right) = \frac{1}{1} = 1.$$

whereas inputs 3 and 4 will multiply an input voltage by 10.

$$\left(\frac{R5}{R3 \text{ or } R4}\right) = \frac{1}{0.1} = 10.$$

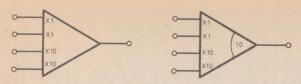

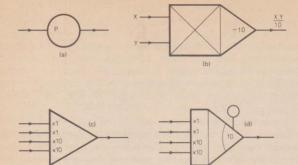

With capacitor C1 selected in the feedback loop, the computing element is converted to an integrator and if values are substituted in the equation for the integrator, it can again be shown that inputs 1, 2 and 3, 4 give a gain of 1 and 10 respectively. The selection of C2 in the feedback loop increases the gain of all inputs by a factor of 10. This is usually referred to as a nose gain of 10. The symbols used to denote adders and integrators with the relevant gain values are shown in Fig. 2.2.

The "Initial Condition" resistors R6 and R7 are brought into the circuit by means of switches RLA2 and S1d. VR1 is a  $10k\Omega$  potentiometer, which provides the op-amp with external offset nulling. This is connected across pins 1 and 5,

with the pot slider taken to the negative supply rail. The non-inverting input of the op-amp is grounded via R8. The value of this resistor should be chosen for good thermal drift performance. The optimum resistance would be equal to the parallel value of the input and feedback resistances. Since in this case there are two values of input resistances, a compromise solution is necessary.

The circuit of Fig. 2.1 represents just one computing element and analogue computers may have many such elements. The prototype has ten computing amplifiers which is an adequate number for the solution of fairly complex problems.

Fig. 2.1. Circuit diagram showing one of the ten computing elements of the Analogue Computer

PART 2

AVING formed a general picture of the workings of the analogue computer, the complete circuit of a computing element can now be described. This is shown in Fig. 2.1. The basic circuits of input and feedback, components connected around the op-amp can be readily recognised. The input comprises four resistors, R<sub>1</sub> to R<sub>4</sub>, which are connected to sockets in the patch panel and to the inverting input of the op-amp, via switches RLA2, S1c, and S1b. The feedback circuit consists of R5, C1 and C2, which can be selected by means of switch S1a and sockets (C7, B6 and C6) on the patch panel.

Consider switch S1a set so that R5 is selected in the feedback loop. The computing element now becomes a summer. By recalling the equation for the addition circuit that was described last month and by substituting the values for R5, R1, R2, R3, and R4 it can be seen that a voltage applied at inputs 1 and 2 will be multiplied by unity,

$$\left(\frac{R5}{R1 \text{ or } R2}\right) = \frac{1}{1} = 1.$$

whereas inputs 3 and 4 will multiply an input voltage by 10.

$$\left(\frac{R5}{R3 \text{ or } R4}\right) = \frac{1}{0.1} = 10.$$

With capacitor C1 selected in the feedback loop, the computing element is converted to an integrator and if values are substituted in the equation for the integrator, it can again be shown that inputs 1, 2 and 3, 4 give a gain of 1 and 10 respectively. The selection of C2 in the feedback loop increases the gain of all inputs by a factor of 10. This is usually referred to as a nose gain of 10. The symbols used to denote adders and integrators with the relevant gain values are shown in Fig. 2.2.

The "Initial Condition" resistors R6 and R7 are brought into the circuit by means of switches RLA2 and S1d. VR1 is a  $10k\Omega$  potentiometer, which provides the op-amp with external offset nulling. This is connected across pins 1 and 5,

with the pot slider taken to the negative supply rail. The non-inverting input of the op-amp is grounded via R8. The value of this resistor should be chosen for good thermal drift performance. The optimum resistance would be equal to the parallel value of the input and feedback resistances. Since in this case there are two values of input resistances, a compromise solution is necessary.

The circuit of Fig. 2.1 represents just one computing element and analogue computers may have many such elements. The prototype has ten computing amplifiers which is an adequate number for the solution of fairly complex problems.

Fig. 2.1. Circuit diagram showing one of the ten computing elements of the Analogue Computer

Fig. 2.2. Symbols used to denote adders and integrators

Mode Control is achieved by means of relay contacts RLA2 and RLB2. Relays are necessary because all ten amplifiers need to be controlled simultaneously. Table 1 shows the positions of relay and other switches for mode control of summers and integrators.

| SWITCH |         | SUMMER |       | INTEGRATOR |      |       |  |  |  |

|--------|---------|--------|-------|------------|------|-------|--|--|--|

|        | COMPUTE | HOLD   | RESET | COMPUTE    | HOLD | RESET |  |  |  |

| RLA2   | 1       | 2      | 2     | 1          | 2    | 2     |  |  |  |

| RLB2   | 1       | 1      | 2     | 1          | 1    | 2     |  |  |  |

| S1a    | OPEN    |        |       | CLOSED     |      |       |  |  |  |

| S1b    | OPEN    |        |       | CLOSED     |      |       |  |  |  |

| S1c    |         | CLOSED |       |            | OPEN |       |  |  |  |

| S1d    | 1       | 1      | 1     | 2          | 2    | 2     |  |  |  |

TABLE 1

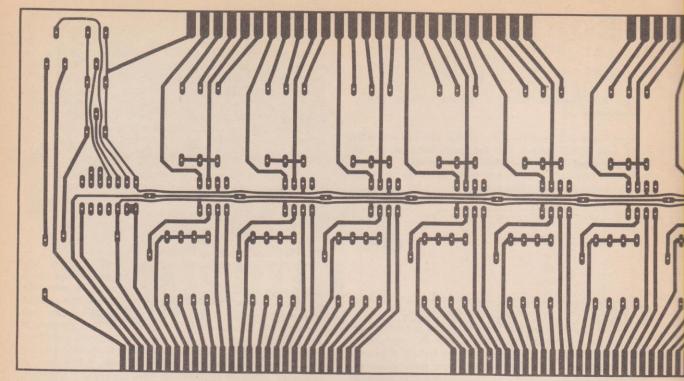

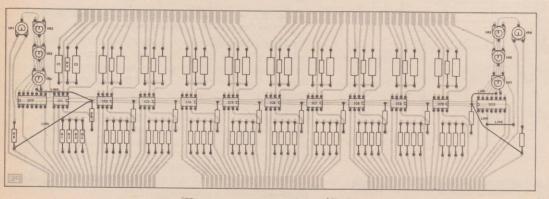

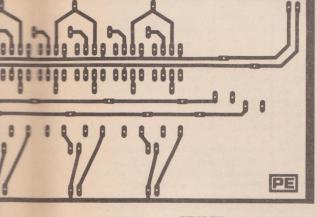

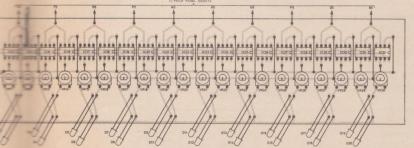

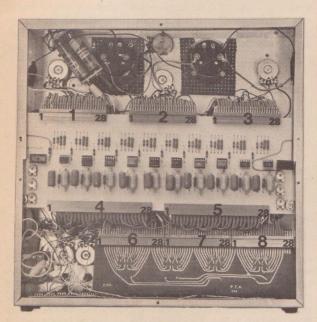

Fig. 2.5 shows how the ten computing amplifiers are arranged on a printed circuit board with the component overlay shown in Fig. 2.7. At the extreme ends of the board the two four-quadrant multiplier i.c.s are accommodated. This main p.c.b. is connected to other points in the computer by means of edge connectors.

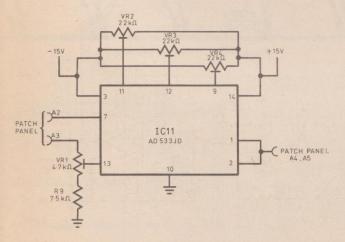

### **The Four-Quadrant Multipliers**

So far it has been shown how to multiply a variable voltage by a constant. This is easily done, using the coefficient multiplier, in conjunction with the amplifier gain. The formation of the product of two variables is much more difficult to obtain. Of the many methods that have been devised, most have involved the use of devices with certain characteristics, e.g. a diode function generator can be set up to provide a square law action, or a log-antilog action. Opamps are usually employed with these circuits.

For the sake of simplicity and compactness it was decided to use two four-quadrant multiplier i.c.s in the prototype. As their name implies these can multiply in four quadrants,

Fig. 2.3. Circuit diagram of the Four Quadrant Multiplier

which means that either or both voltages can be positive or negative. This dispenses with the need to have an absolute value circuit preceding the multiplier, as is the case with other methods.

The particular device chosen for the prototype was the AD533JD integrated circuit (shown in Fig. 2.3). This is not the cheapest four-quadrant multiplier on the market, but it has the advantage of being simple to operate, with the minimum of external components. The i.c. comprises a transconductance multiplying element, a stable reference, and an output operational amplifier on a single monolithic silicon chip.

The AD533JD multiplies with a transfer function of  $\frac{XY}{10}$ . The division by 10 should not worry the programmer but it should always be borne in mind when solving a problem. The op-amp output provides  $\pm 10V$  at 5mA, and is fully protected against short circuits to ground or either supply voltage. The inputs are fully protected against overvoltage transients.

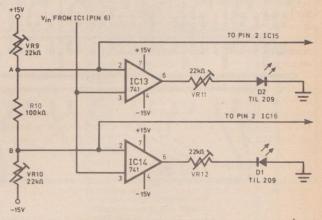

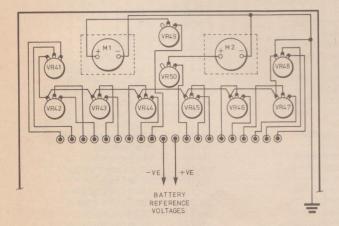

### **The Overload Warning Circuit**

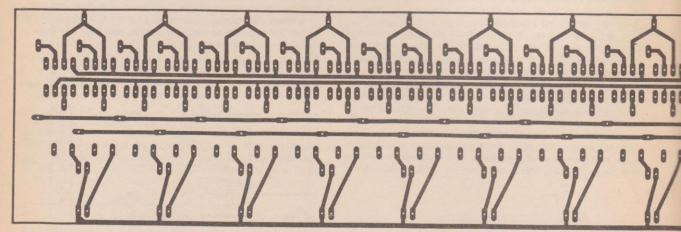

The operation of the overload warning circuit is very simple. The output of every computing amplifier is sampled and compared with a positive and a negative reference voltage. If the amplifier output goes higher than the positive reference voltage, an l.e.d. is switched on, to indicate that the amplifier is saturating in the positive sense. Similarly, if the amplifier output falls below the negative reference voltage another l.e.d. is switched on to indicate saturation in the negative sense. The prototype uses ±11V as the reference voltages. An overload warning circuit is shown in Fig. 2.4. Only one pair of comparators and l.e.d.s are shown but ten pairs are necessary to serve the ten computing amplifiers. This circuit is arranged on a separate p.c.b. shown in Fig. 2.6 with the component overlay shown in Fig. 2.8.

Fig. 2.4. Circuit diagram of the Overload Warning system required for each computing element

Resistor R9 and potentiometers VR11 and VR12 are connected across the positive and negative supply rails to form a potential divider that generates the positive and negative reference voltages of +11V and -11V. These voltages are applied to the inverting inputs of the twenty comparators as shown. The output of each computing amplifier is applied to the non-inverting inputs of the corresponding pair of comparators. The comparators drive the warning l.e.d.s, the brightness of which is set by preset potentiometers. The 741 op-amp was also used here as a comparator. Experience with the prototype has shown that the 741 is capable of driving the l.e.d.s with reasonable brightness without overheating.

Fig. 2.5. Main p.c.b. containing the ten computing elements and the two F

Fig. 2.6. The Overload Warning p.c.b.

Fig. 2.7. Component layout for the main p.c.b.

Fig. 2.8. Component layout for the Overload Warning Circuit

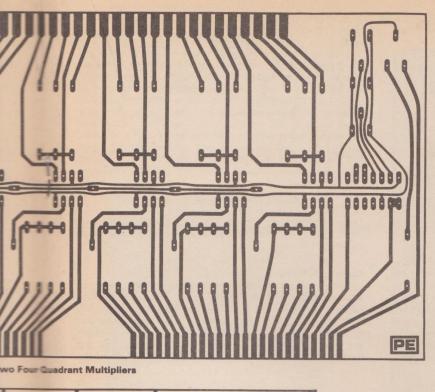

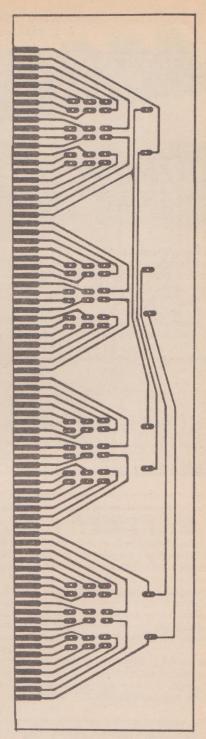

Fig. 2.9. P.c.b. design for the Relay Board

### The Relay Mode Control P.C.B.

With ten amplifiers and two relay contacts per amplifier there is a need for twenty relay contacts. Complete mode control could be achieved with two ten-pole relays, one operating the RLA and C switches and the other the RLB and D switches. Ten-pole relays are difficult to find however and the prototype uses four six-pole relays operating in pairs. (The coil connections for the four relays are shown in Fig. 2.11.) This arrangement leaves four unused poles, which may become useful if it is decided to extend the computer.

Fig. 2.11. Coil diagram for relays

The p.c.b. which accommodates the four relays is shown in Fig. 2.9. Connections to and from this board are also made via edge connectors.

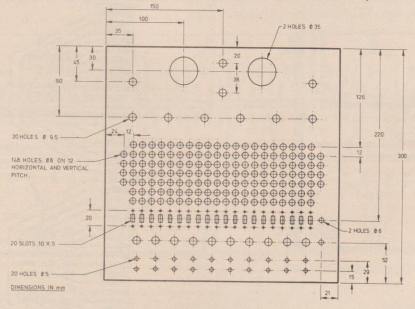

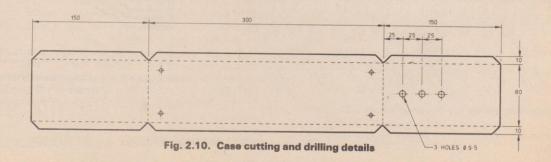

### **Case Construction**

The front panel requires a large surface area to accommodate the patch panel, potentiometers, switches, l.e.d.s etc. Because of this it will be difficult to obtain the right shaped case off the shelf. The prototype case was constructed from aluminium sheet. Two square panels form the front and the back of the case and the sides, top and bottom are cut and shaped as shown in Fig. 2.10, using the

same gauge aluminium sheet. A bench vice, folding bar, and a sheet metal mallet are useful for this purpose. Fig. 2.10 shows the positions and dimensions of the holes required in the front panel. A lot of patience is required for the process of drilling, due to the large number of holes and the fact that a badly positioned hole will be detrimental to the appearance of the layout. This is particularly true in the case of the patch panel holes. A pitch of 12mm in both directions is enough to give a reasonable tolerance for positioning errors and at the same time avoid excessive gaps between the sockets. For the larger holes the use of sheet metal punches is recommended. Having drilled or punched all the holes, the front panel should then be labelled using dry letter transfers and sprayed with a clear lacquer fixative. The suggested labelling is shown in the photograph of the front panel.

### The Patch Panel

The patch panel is constructed using 3.2mm sockets arranged in a matrix and packed together as closely as possible. There are 148 of these sockets and because identifying each one is difficult a colour coding system was used. Fig. 2.12 shows the arrangement of the sockets for one amplifier, one coefficient multiplier and one four-quadrant multiplier.

The pattern for the amplifier and coefficient multiplier shown, in Fig. 2.12 is repeated ten times for the ten computing elements. The eight coefficient multipliers use 16 sockets on the top row. Two of the remaining four sockets are connected to the two panel meters and the other two are connected to batteries to provide reference voltages. Both positive and negative reference voltages will be needed for the solution of certain problems.

|    | GO | RO |

|----|----|----|

| vo |    | ВО |

| GO | 0  | OR |

| RO | 0  | RO |

| RO | 1  | RO |

|    |    | GO |

|    | RO | 0  |

Fig. 2.12. Patch panel layout for one computing element (rows B and C) and one Four Quadrant Multiplier (row A)

For the four-quadrant multipliers four sockets are needed per multiplier and these are positioned on the extreme left and right of the patch panel.

### COMPONENTS . . .

### Resistors

R1, R2, R5 1MΩ  $\frac{1}{2}$ W 2% metal oxide (30 off) R3, R4 100kΩ  $\frac{1}{4}$ W 2% metal oxide (20 off) R8 270kΩ  $\frac{1}{4}$ W 5% carbon (10 off) R9 100kΩ  $\frac{1}{2}$ W 5% carbon (2 off)

### **Potentiometers**

$\begin{array}{lll} VR1, VR8 & 4.7k\Omega \ (2\ off) \\ VR2-VR7 & 22k\Omega \ (6\ off) \\ VR9-VR30 & 22k\Omega \ (22\ off) \\ VR31-VR40 & 10k\Omega \ 0.5W \ Lin \ (10\ off) \end{array}$

All horizontal min. presets except where stated

### Capacitors

C1 1μF 160V (10 off) C2 0·1μF 160V (10 off)

### Semiconductors

IC1-IC30 741 op amp (30 off) IC31-IC32 AD533JD (2 off) D1-D20 TIL 209 (20 off)

### Miscellaneous

4 off 6 way changeover relays 4 off mounting sockets for relays holders for i.c.s (if req.)

CONSTRUCTOR'S NOTE: The AD533JD Four Quadrant Multiplier is available from Analog Devices Ltd., Central Avenue, East Molesey, Surrey.

### Stage by Stage Construction

The computer has been designed so that it can be built in stages. At this point in the construction, ie, with the aluminium case and the p.c.b.s constructed and drilled, the constructor has to take a decision, as to whether he wants to opt for a stage construction. His choice can be very flexible. For example, one may decide that initially, all ten computing amplifiers are not absolutely necessary for the solution of simple problems with which the inexperienced programmer will be involved. Four amplifiers are enough to carry out fairly interesting experiments. Later, when more experience is gained, more computing amplifiers can be added as necessary. The same applies to the coefficient multipliers and the panel meters.

It should be mentioned that if four 6-pole relays are used for the mode control, as is the case with the prototype, at least two of these will be necessary even if only one or two amplifiers are used initially. Two 6-pole relays can provide mode control for six amplifiers.

Another area in which stage by stage construction can be applied, concerns the overload warning circuit. Here, the comparators and the l.e.d.s can be added following the addition of more amplifiers. Alternatively it may be decided to leave the warning circuit out altogether initially. This will make life difficult for the programmer, but it will not affect the operation of the computer.

**NEXT MONTH: WIRING AND TESTING**

### ELECTRONICS

VOLUME 14 No.15 NOVEMBER 1978

| CONSTRUCTIONAL PROJECTS                                                                                           |              |

|-------------------------------------------------------------------------------------------------------------------|--------------|

| MOON LANDING GAME by A. Russell Sixty seconds to avoid a negative altitude situation                              | 1138         |

| P.E. V.D.U. SYSTEM—2 by A. A. Berk, B.Sc., Ph.D.  Construction and setting up  PROXIMITY SWITCH by A. K. Langford | 1146         |

| A variable sensitivity touch and proximity switch  ANALOGUE COMPUTER—3 by P. J. Kronis, B.Sc.                     | 1160         |

| Wiring, testing and programming WIDE RANGE C/R BRIDGE by W. English                                               | 1165         |

| 1000μF/10ΜΩ                                                                                                       | 1180         |

| GENERAL FEATURES                                                                                                  |              |

| POWER FETs by David Shortland The latest developments in field effect technology INGENUITY UNLIMITED              | 1154         |

| 741 Supply—Soldering Iron Simmer Control—Auto-Tune Generator—Touch Tuner                                          | 1173         |

| NEWS AND COMMENT                                                                                                  |              |

| EDITORIAL                                                                                                         | 1137         |

| Two irons at special prices                                                                                       | 1143         |

| SPACEWATCH by Frank W. Hyde                                                                                       | 1140         |

| German Satellite, U.S. Satellite, TDRSS, Pioneer Venus 2, TRS, Intelsat Terminal, Spacelab 2  NEWS BRIEFS         | 1144         |

| Starlight Vision                                                                                                  | 1153         |

| Bubbling with Bits—Blinking Good—On the Levell Data Encryption Unit                                               | 1170<br>1182 |

| MARKET PLACE                                                                                                      |              |

| New products                                                                                                      |              |

| SEMICONDUCTOR UPDATE by R. W. Coles A look at some recently released devices                                      | 1179         |

| STATESIDE SCENE by Dave Coutts                                                                                    |              |

| New York News                                                                                                     | 1182         |

| SPECIAL SUBSCRIPTION OFFER                                                                                        | 1185         |

| INDUSTRY NOTEBOOK by Nexus What's happening inside industry                                                       | 1186         |

| PATENTS REVIEW                                                                                                    |              |

| Thought provoking ideas on file at the British Patents Office                                                     | 1187         |

| A selection of readers' letters                                                                                   | 1188         |

| POINTS ARISING                                                                                                    | 1188         |

|                                                                                                                   |              |

### **SPECIAL 8-PAGE SUPPLEMENT**

**CAR DEVICES** Auto-Light—Vari-Wipe—Assisted Ignition System—Intruder Alarm—Battery State Indicator—Polarity Inverter between 1164 and 1165

Our December issue will be on sale Friday, 10 November 1978

(for details of contents see page 1145)

© IPC Magazines Limited 1978. Copyright in all drawings, photographs and articles published in PRACTICAL ELECTRONICS is fully protected, and reproduction or imitations in whole or part are expressly forbidden. All reasonable precautions are taken by PRACTICAL ELECTRONICS to ensure that the advice and data given to readers are reliable. We cannot, however, guarantee it, and we cannot accept legal responsibility for it. Prices quoted are those current as we go to press.

Practical Electronics November 1978

- **★** Wiring

- \* Testing

- \* Programming

P. J. KRONIS B.Sc.

PART 3

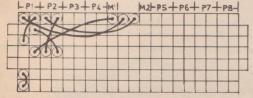

AFTER the p.c.b.s have been assembled and checked, all the components should be fitted into the case with the overload warning p.c.b. mounted on the base of the box using 6BA screws. With all the components mounted in the case the coefficient multipliers and the two panel meters should be wired first, following the wiring diagram shown in Fig. 3.1. Resistors R6, R7 and the links shown in Fig. 3.2 should be wired to each of the ten computing amplifiers. The wiring to the relay board and main p.c.b. is via eight edge connectors and to ease the problem of wiring these connectors a wiring schedule is given in Fig. 3.3. The numbering and layout arrangement of the patch panel and switches is given in Fig. 3.4.

The main p.c.b. is mounted above the patch panel and the relay board above the offset null potentiometers as shown in the photograph. After the computer wiring has been completed and checked a  $\pm 15$ V power supply should be connected to the unit and the following test procedures followed.

Fig. 3.1. Wiring diagram for the coefficient multipliers and panel meters

### THE OFFSET NULL TRIM PROCEDURE

Set all the amplifiers to "add" by pushing all the slide switches down. Put the computer into the "compute" mode using the mode control switch and turn the sensitivity of the meters down as far as possible. Connect the output of the first amplifier (A1) to meter 1 (M1). Ground one of the ×10 inputs of A1. This can be done by touching one end of the wire lead on the case. Connect the power supply and switch on. Increase the sensitivity of M1 gradually until the needle deflects to maximum if possible. Bring the needle back to by adjusting the offset null potentiometer of amplifier A1. Increase the sensitivity of the meter and repeat the same procedure until the needle is on zero when the meter is at maximum sensitivity.

Decrease the sensitivity fully and repeat the trim procedure for all amplifiers in the same way.

X and Y inputs Common outputs Coefficient multiplier input Coefficient multiplier output Initial conditions **Amplifier** outputs **Amplifier** inputs (X1) **Amplifier** inputs (X10) Spare socket Integrate with nose gain of one Integrate with nose gain of ten

Fig 3.2. Link wiring for amplifiers and multipliers

| Edge Connector 1 From To                |                                           | pin 13           | U3 Patch Panel                   | Edge Connector 6 |                                       |  |  |  |

|-----------------------------------------|-------------------------------------------|------------------|----------------------------------|------------------|---------------------------------------|--|--|--|

| pin 3                                   | To<br>A3 Patch Panel                      | pin 14<br>pin 15 | U2 Patch Panel                   | From             | То                                    |  |  |  |

| pin 3                                   | Earth                                     | pin 16           | TB9 Terminal Block<br>VR59       | pin 3            | -15V Supply                           |  |  |  |

| pin 5                                   | A2 Patch Panel                            | pin 17           | Edge Connector 5 pin 27          | pin 4            | S2c Common                            |  |  |  |

| pin 6                                   | -15V Supply                               | pin 18           | W5 Patch Panel                   | pin 5            | S1c Common                            |  |  |  |

| pin 7                                   | A4 Patch Panel                            | pin 19           | W4 Patch Panel                   | pin 9            | TB1 Terminal Block                    |  |  |  |

| pin 8                                   | Edge Connector 6 pin 10                   | pin 20           | W3 Patch Panel                   | pin 10           | S1b Add                               |  |  |  |

| pin 9                                   | C5 Patch Panel                            | pin 21           | W2 Patch Panel                   | pin 11           | S2b Add                               |  |  |  |

| pin 10                                  | C4 Patch Panel                            | pin 22           | TB10 Terminal Block              | pin 12           | TB2 Terminal Block                    |  |  |  |

| pin 11                                  | C3 Patch Panel                            | pin 23           | VR60                             | pin 13           | TB3 Terminal Block                    |  |  |  |

| pin 12                                  | C2 Patch Panel                            | pin 24           | X2 Patch Panel                   | pin 14           | S3b Add                               |  |  |  |

| pin 13                                  | TB1 Terminal Block                        | pin 25           | X4 Patch Panel                   | pin 15<br>pin 16 | S4b Add                               |  |  |  |

| pin 14                                  | VR51                                      | pin 27           | X3 Patch Panel                   | pin 17           | TB4 Terminal Block TB5 Terminal Block |  |  |  |

| pin 15                                  | Edge Connector 6 pin 11                   |                  |                                  | pin 18           | S5b Add                               |  |  |  |

| pin 16                                  | E5 Patch Panel                            | Edge Co          | nnector 4                        | pin 19           | S5a Common                            |  |  |  |

| pin 17                                  | E4 Patch Panel                            | From             | То                               | pin 20           | S4c Common                            |  |  |  |

| pin 18                                  | E3 Patch Panel                            | pin 2            | +15V Supply                      | pin 21           | S3c Common                            |  |  |  |

| pin 19                                  | E2 Patch Panel                            | pin 3            | VR51                             | pin 22           | S11a Compute                          |  |  |  |

| pin 20                                  | TB2 Terminal Block                        | pin 4            | B6 Patch Panel                   | pin 23           | TB2 Terminal Block                    |  |  |  |

| pin 21                                  | VR52                                      | pin 5            | S1d Add                          | pin 24           | TB1 Terminal Block                    |  |  |  |

| pin 22                                  | Edge Connector 6 pin 14                   | pin 6            | B5 Patch Panel                   | pin 28           | Earth, Edge Connector 7 pin 3         |  |  |  |

| pin 23                                  | G5 Patch Panel                            | pin 7            | C6 Patch Panel                   |                  |                                       |  |  |  |

| pin 24                                  | G4 Patch Panel                            | pin 8            | VR52                             | Edga Ca          |                                       |  |  |  |

| pin 25                                  | G3 Patch Panel                            | pin 9            | D6 Patch Panel                   |                  | nnector 7                             |  |  |  |

| pin 26<br>pin 27                        | G2 Patch Panel<br>TB3 Terminal Block      | pin 10           | S2d Add                          | From             | То                                    |  |  |  |

| pin 28                                  | VR53                                      | pin 11           | D5 Patch Panel                   | pin 1            | S1a Integrate                         |  |  |  |

| piii 20                                 | V1105                                     | pin 12           | E6 Patch Panel                   | pin 2            | S2a Integrate                         |  |  |  |

| Edge Cor                                | mector 2                                  | pin 13           | VR53                             | pin 3            | Edge Connector 7 pin 4                |  |  |  |

| From                                    | To                                        | pin 14           | F6 Patch Panel                   | pin 4<br>pin 5   | Edge Connector 7 pin 7                |  |  |  |

|                                         |                                           | pin 15           | S3d Add                          | pin 6            | S3a Integrate S4a Integrate           |  |  |  |

| pin 1                                   | Edge Connector 6 pin 15                   | pin 16           | F5 Patch Panel                   | pin 7            | Edge Connector 7 pin 8                |  |  |  |

| pin 2<br>pin 3                          | J5 Patch Panel<br>J4 Patch Panel          | pin 17           | G6 Patch Panel<br>VR54           | pin 8            | Edge Connector 8 pin 9                |  |  |  |

| pin 4                                   | J3 Patch Panel                            | pin 18<br>pin 19 | H6 Patch Panel                   | pin 9            | S5a Integrate                         |  |  |  |

| pin 5                                   | J2 Patch Panel                            | pin 20           | S4d Add                          | pin 10           | TB5 Terminal Block                    |  |  |  |

| pin 6                                   | TB4 Terminal Block                        | pin 21           | H5 Patch Panel                   | pin 11           | TB4 Terminal Block                    |  |  |  |

| pin 7                                   | VR54                                      | pin 22           | J6 Patch Panel                   | pin 12           | TB3 Terminal Block                    |  |  |  |

| pin 8                                   | Edge Connector 6 pin 18                   | pin 23           | VR55                             | pin 13           | S7c Common                            |  |  |  |

| pin 9                                   | L5 Patch Panel                            | pin 24           | K6 Patch Panel                   | pin 14           | S6c Common                            |  |  |  |

| pin 10                                  | L4 Patch Panel                            | pin 25           | S5d Add                          | pin 18           | TB6 Terminal Block                    |  |  |  |

| pin 11                                  | L3 Patch Panel                            | pin 26           | K5 Patch Panel                   | pin 19           | S6b Add                               |  |  |  |

| pin 12                                  | L2 Patch Panel                            | pin 27           | L6 Patch Panel                   | pin 20           | S7b Add                               |  |  |  |

| pin 13                                  | TB5 Terminal Block                        |                  |                                  | pin 21           | TB7 Terminal Block                    |  |  |  |

| pin 14                                  | VR55                                      | Edge Co          | nnector 5                        | pin 22           | TB8 Terminal Block                    |  |  |  |

| pin 15                                  | Edge Connector 5 pin 19                   | From             | То                               | pin 23           | S8b Add                               |  |  |  |

| pin 16                                  | N5 Patch Panel                            |                  |                                  | pin 24           | S9b Add                               |  |  |  |

| pin 17                                  | N4 Patch Panel                            | pin 2            | VR56                             | pin 25           | TB9 Terminal Block                    |  |  |  |

| pin 18                                  | N3 Patch Panel                            | pin 3            | M6 Patch Panel                   | pin 26           | TB10 Terminal Block                   |  |  |  |

| pin 19                                  | N2 Patch Panel                            | pin 4            | S6d Add                          | pin 27           | S10b Add                              |  |  |  |

| pin 20                                  | TB6 Terminal Block                        | pin 5            | M5 Patch Panel                   | pin 28           | S10c Common                           |  |  |  |

| pin 21                                  | VR56                                      | pin 6            | N6 Patch Panel                   |                  |                                       |  |  |  |

| pin 22                                  | Edge Connector 5 pin 20                   | pin 7            | VR57                             | Edge Co          | nnector 8                             |  |  |  |

| pin 23<br>pin 24                        | Q5 Patch Panel<br>Q4 Patch Panel          | pin 8            | P6 Patch Panel                   | From             | То                                    |  |  |  |

| * 11 1000000000000000000000000000000000 |                                           | pin 9            | S7d Add                          | pin 1            | S9c Common                            |  |  |  |

| pin 25<br>pin 26                        | Q3 Patch Panel                            | pin 10           | P5 Patch Panel                   | pin 2            | S8c Common                            |  |  |  |

| pin 27                                  | Q2 Patch Panel<br>TB7 Terminal Block      | pin 11           | Q6 Patch Panel                   | pin 3            | +15V Supply                           |  |  |  |

| pin 28                                  | VR57                                      | pin 12           | VR58                             | pin 4            | TB7 Terminal Block                    |  |  |  |

| piii 20                                 | V1107                                     | pin 13           | R6 Patch Panel                   | pin 5            | TB6 Terminal Block                    |  |  |  |

| Edge Connector 3                        |                                           | pin 14           | S8d Add                          | pin 9            | Edge Connector 8 pin 12               |  |  |  |

| From                                    | To                                        | pin 15           | R5 Patch Panel                   | pin 10           | S6c Integrate                         |  |  |  |

| pin 3                                   |                                           | pin 16           | S6 Patch Panel                   | pin 11           | S7a Integrate                         |  |  |  |

| pin 3                                   | Edge Connector 5 pin 23<br>S5 Patch Panel | pin 17           | VR59                             | pin 12           | Edge Connector 8 pin 13               |  |  |  |

| pin 4<br>pin 5                          | S4 Patch Panel                            | pin 18           | T6 Patch Panel                   | pin 13           | Edge Connector 8 pin 16               |  |  |  |

| pin 6                                   | S3 Patch Panel                            | pin 19           | S9d Add                          | pin 14           | S8a Integrate                         |  |  |  |

| pin 7                                   | S2 Patch Panel                            | pin 20<br>pin 21 | T5 Patch Panel<br>U6 Patch Panel | pin 15           | S9a Integrate                         |  |  |  |

| pin 8                                   | TB8 Terminal Block                        | pin 21           | VR60                             | pin 16           | Edge Connector 8 pin 17               |  |  |  |

| pin 9                                   | VR58                                      | pin 23           | V6 Patch Panel                   | pin 18           | S10a Integrate                        |  |  |  |

| pin 10                                  | Edge Connector 5 pin 24                   | pin 23           | S10d Add                         | pin 19           | TB10 Terminal Block                   |  |  |  |

| pin 11                                  | U5 Patch Panel                            | pin 25           | V5 Patch Panel                   | pin 20<br>pin 21 | TB9 Terminal Block TB8 Terminal Block |  |  |  |

| pin 12                                  | U4 Patch Panel                            | pin 26           | W6 Patch Panel                   | pin 21           | Reset Switch (S12)                    |  |  |  |

|                                         |                                           |                  |                                  | PITZZ            | neset owner (o 12)                    |  |  |  |

| Fig. 3.3. Wiring Schedule               |                                           |                  |                                  |                  |                                       |  |  |  |

### Wiring Schedule—cont.

### From

S1b, S1d Common S2b, S2d Common S3b, S3d Common S4b,S4d Common S5b, S5d Common S6b, S6d Common S7b, S7d Common S8b, S8d Common S9b, S9d Common S10b, S10d Common Reset Button (S12) S11a S11b —15V Supply

VR51 Wiper

To TB1 Terminal Block TB2 Terminal Block TB3 Terminal Block TB4 Terminal Block TB5 Terminal Block TB6 Terminal Block **TB7 Terminal Block** TB8 Terminal Block TB9 Terminal Block TB10 Terminal Block S11b Compute +15V Supply -15V Supply VR51 Wiper VR52, 53, 54, 55, 56,

57, 58, 59, 60 (Wipers)

Fig. 3.4. Layout arrangements for edge connectors, patch panel and switches

### **MODE CONTROL TEST**

Set amplifier A1 to "integrate", and the mode to "compute" and monitor the output with one of the meters. Apply a voltage to a ×1 input. The needle should deflect gradually in the positive direction, if the applied input voltage is negative, and vice-versa, until the amplifier saturates. When this happens, adjust the meter sensitivity so that the needle is at maximum deflection. Put the computer in the "hold" mode and press the "reset" switch. The needle should go to zero. Release "reset" and switch to "compute" The needle will again start to deflect and this time switch the mode to "hold" before the amplifier saturates. The needle should then stop moving. Carry out this test with all the amplifiers. While doing this, observe the operation of the overload warning circuit. The appropriate l.e.d. should come on when the amplifier output exceeds +11V or goes below -11V. Check both positive and negative operation by applying both positive and negative input voltages.

The above tests are not complete by any means but any remaining problems will show up when the examples described under "programming" are attempted.

### COMPONENTS . . .

### Resistors

R6, R7 100kΩ ¼W carbon (2 off)

### Potentiometers

VR41–VR48 100 k $\Omega$  linear (8 off) VR49–VR50 300 k $\Omega$  linear (2 off)

### Miscellaneous

1 off d.p.d.t. switch (R.S. type 316-793)

20 off d.p.d.t. sub-min slide switch

2 off 50-0-50µA (ME15 T40 Watford Electronics)

1 off Push button (R.S. type 337-914)

151 off Square 4mm panel mounted sockets (55 red, 32

yellow, 22 green, 21 white, 21 black) 8 off Skirted knob

12 off Plain knob

6 off 28 way edge connector 0.1in matrix

2 off 28 way edge connector 0.15in matrix

Banana plugs (as required)

### **PROGRAMMING**

It has already been mentioned, that it is necessary to form a mathematical model of the problem to be solved and the computer cannot help us to do this, but being very faithful however, it will happily try to solve a problem even if the wrong information is fed into it. Fortunately, in such cases the programmer could get an indication that something had gone wrong by studying the results which are usually meaningless. The general rule "Garbage In, Garbage Out" (well known to digital computer programmers) applies here also. Unfortunately, error checks cannot be incorporated in the analogue programs, as is the case with digital programs. It is important therefore to adopt a methodical procedure for programming to avoid errors.

Having formed the mathematical model, the equations are rearranged and a flow diagram is constructed which satisfies the equations. All values to be input and all computing elements to be used, are marked on the flow diagram to avoid confusion, Referring to the diagram the computer is then programmed by patching the panel. This procedure will be illustrated by several examples. The flow diagrams are constructed using standard symbols representing computing elements. Some of these have already been given. Fig. 3.5 shows all the symbols to be used in this article.

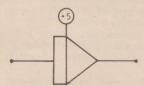

Fig. 3.5. Computing element symbols: (a) coefficient multiplier; (b) Four quadrant multiplier; (c) Summer; (d) Integrator with initial conditions.

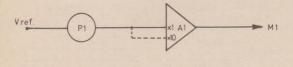

As a first example let us examine the operation of potentiometers, adders and integrators, using simple experiments.

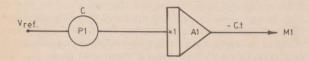

Apply a reference voltage to the input of P1 and connect the output to M1. Adjust the sensitivity of M1 so that when P1 is at maximum, M1 deflects fully. Operate the potentiometer and observe the results.

Switch the power on and calibrate M1 by applying a known voltage (e.g. supply voltage), to read 15V at full deflection. Switch A1 to "add" and apply the output of P1 to the input of A1 and the output of A1 to M1. The flow diagram and patch panel connections are shown in Fig. 3.6. Test all A1 inputs in turn and observe the gain of the adder each time.

Fig. 3.6. Flow diagram and patch panel layout for the potentiometer example

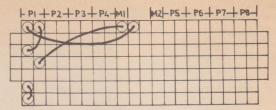

To examine the operation of the integrators, we can integrate various functions and study the results. First let us see what happens when we integrate a constant, C. The mathematicians will immediately give us the answer as C.t + K, where t is the variable (time in this case) and K is another constant. This is a straight line, of gradient C and passing through the origin, if we have no initial conditions, i.e. C=0 at t=0. To verify this we can set up the program shown in Fig. 3.7.

Fig. 3.7. Flow diagram and patch panel layout for the integration example

To run this program follow these steps:

- (1) Check A1 is in "integrate"

- (2) Computer mode: "hold"

- (3) Switch power on

- (4) Press reset for a few seconds and release

- (5) Switch to "compute" and observe the meter.

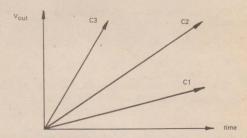

Vary the value of C by adjusting P1 and repeat the above steps. If an X-Y plotter is available the results can be plotted for different values of C. The graph would look like Fig. 3.8. With C set to 1 volt the output should increase at 1 volt per second (C=C.t). This can be verified by timing the deflection of the needle.

Fig. 3.8. Graph showing the resultant curves when various values for the constant C are integrated

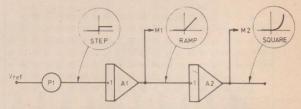

These examples serve to illustrate the use of the analogue computer as a function generator. By integrating a step function we obtained a ramp function, the slope of which we could easily control. The ramp function can be integrated again to produce a square law function. This is shown in the flow diagram in Fig. 3.9. Still higher power functions can be obtained by successive integrations.

Fig. 3.9. By integrating waveforms the analogue computer can be used as a function generator

### INITIAL CONDITIONS EXAMPLE

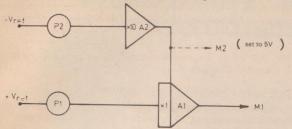

In the previous integrator examples we assumed that at time t=0 all variables had zero value. Suppose that we wanted to give a value to the output of the integrator, before the computation begins. It is not difficult to imagine examples where this might be used. We may for example like to investigate the flight of a rocket, not from the point of launch but from some height above the launching pad, at which the rocket will have some velocity and acceleration. To illustrate the use of initial conditions we can repeat the first integrator example, but this time we are going to give an initial value to the integrator output of 5V. We therefore

require 5V to be applied to the initial condition socket of A1. Since the value of the reference voltages is only about 1.5V, we shall have to multiply this value. This we can do with the aid of an adder and a potentiometer. The flow diagram and patch panel connections are shown in Fig. 3.10.

Fig. 3.10. Flow diagram and patch panel layout for the initial condition example

To run this program follow these steps after the panel has been patched.

- (1) Switch power on

- (2) Amplifier A1 integrating and A2 adding

- (3) Computer mode: "hold"

- (4) Monitor A2 output and adjust to 5V using P2

- (5) Set output of P1 to 1V

- (6) Press "reset" for a few seconds and release (Output of A1 should now show 5V)

- (7) Switch mode to "compute" and observe M1.

The initial condition value is invariably formed using an adder and a potentiometer, unless of course the exact value is available. It is therefore common practice not to show these two computing elements, but simply to note the value being applied to the initial condition socket as shown in Fig. 3.11.

Fig. 3.11. Initial condition symbol

Another point worth noting here is that it is not essential for the potentiometer to precede the adder as shown in the flow diagram. In fact in such cases it is better for the amplifier to precede the potentiometer, as the former presents a higher input impedance to the battery than the latter and therefore saves battery energy.

### **ENGINEERING PROBLEMS**

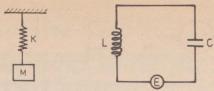

Consider a mass M supported on a spring of stiffness K. If the mass is disturbed, the system will begin to oscillate about the equilibrium position. Mechanical systems usually have electrical equivalents or vice-versa. The electrical equivalent to the spring mass system is the capacitor inductor series circuit. Both systems are shown in Fig 3.12.

The equation of motion of the spring mass system is M  $\ddot{x}$  + K x = 0. The electrical system is described by a similar

Fig. 3.12. The mechanical spring/mass circuit and its electrical equivalent the inductor/capacitor series circuit

equation but with electrical symbols substituted for the mechanical ones. The "dot" notation is used where time derivatives are involved. For example, one dot means the first derivative of the variable in question, with respect to time, two dots mean the second derivative and so on. So if x represents displacement, then  $\dot{x}$  represents velocity, and  $\ddot{x}$  acceleration. The equation can be rearranged so that the highest derivative appears on the left-hand side, with everything else on the right-hand side. This is normal practice when solving a problem on the analogue computer. The

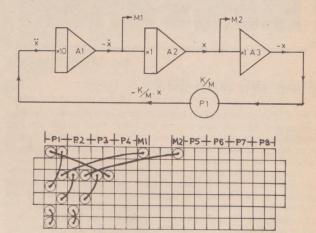

equation becomes  $\ddot{x} = -\frac{K}{M}x$  and the flow diagram is shown in Fig. 3.13.

Fig. 3.13. Flow diagram and patch panel layout for the spring/mass example

By integrating  $\ddot{x}$  twice we obtain  $-\dot{x}$  and x. In our equation, however, we require -x and so A3 is used as a sign inverter. The value K/M is set up on potentiometer P1, the output of which becomes -K/M. x. This is equal to  $\ddot{x}$  and therefore we can close the loop by connecting the output of P1 back to the input of A1. The system as it stands will not vibrate unless it is disturbed. Theoretically once it is disturbed, it should go on vibrating for ever. In practice, however, we know that this is not true, because of the presence of some damping, due to air resistance in the case of the mechanical system and electrical resistance in the case of the electrical system. The analogue computer should produce results very near to the theoretical predictions, i.e. very little damping should be present. To run this program follow these steps.

- (1) Check A1 and A2 are integrating and A3 is adding.

- (2) Switch power on.

- (3) Switch mode to "compute".

- (4) Apply a disturbance to the input of A2 or A3. (This can be done by momentarily touching the input socket, with a wire lead connected to a reference voltage socket. This is equivalent to giving the weight a gentle push.)

- (5) Observe the meters and adjust the sensitivity to produce a reasonable needle deflection.

- (6) Operate P1 and see what happens to the frequency and amplitude of oscillation.

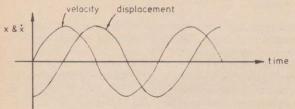

You should find that a high value of K/M (i.e. high spring stiffness or small mass or both) gives a high frequency and vice versa. The other point to note is that the oscillation is sinusoidal. The output of A1 (i.e. the velocity) is a cosine function, whereas that of A2 (the displacement) is a sine

Fig. 3.14. Graph showing the phase difference between velocity and displacement

function. There is a phase difference of 90 degrees between the velocity and the displacement. (The mass comes to a momentary stop when the displacement is at a maximum.) This is shown in the graph in Fig 3.14.

In this last example we have seen how the analogue computer can be used as a function generator for sine or cosine functions, with variable frequency. The frequency of oscillation is given by

$$f = \frac{1}{2\pi} \sqrt{\frac{K}{M}}$$

Hz (cycles per second)

This can be checked by counting the number of cycles in one minute and dividing by 60 to convert to cycles per second. If the value of P1 is set to 1.0 and the input of A1 is multiplying by 10 then K/M = 10 and the frequency should be  $f = 1/2 \sqrt{10} = 0.503$ Hz.

NEXT MONTH: PROGRAMMING AND SPECIAL CIRCUITS (conclusion of series)

### **News Briefs**

by Mike Abbott

### **BUBBLING WITH BITS**

THE IDEA of the magnetic bubble conjures up a picture of quivering clusters gurgling their way to the North Pole. In fact powerful magnetic bubble memories are about to "pop" onto the scene from at least two major electronics manufacturers in the near future, one of which is Texas Instruments.

Sample quantities of a new quarter-million-bit bubble memory will be available from T.I. before the end of this year, but at \$500 each there probably won't be many P.E. constructors in the queue. (A 92k—bit bubble memory is now in volume production at a price of \$100 in 100 unit quantities). The big one however, designated the TIB0303, is full of three micron diameter magnetic bubble domains, and uses separate I/O, minor loop architecture, and features block replication of data. Separate read and write tracks with minor loop data storage are at the heart of this block replicate-based architecture to provide improved performance.

A total of 252 minor loops, each consisting of 1,137 bubble positions, results in a single-chip memory capacity of 286,524 bits. However, 224 loops are utilised resulting in a minimum data capacity of 254,688 bits.

Data bits are written into the write track and exchanged with stored data in the minor loops via swap gates. Data blocks are replicated simultaneously at minor loop and output track junctions, rather than serial duplication which is characteristic of major/minor loop architecture. Consequently, power-down cycle time is significantly reduced from 12.8 milliseconds in the 92K-bit major/minor loop configuration to 12.5 microseconds for block replicate, representing three orders of magnitude improvement.

Other key features include: advanced asymmetric chevron design for improved bubble propagation and transfer, merged data that allows a continuous flow of data bits at the read track, and a dedicated loop for storage of on-chip redundancy information and address synchronisation.

Performance specifications at 100 kilohertz operation are an average access time of 7.3 milliseconds for the first bit of the 224-bit page and a typical power consumption of 0.9 watt for continuous operation. A data-merge function allows a read data of 100K bits per second. Operating temperature is 0° to 50°C with non-volatile storage range of -40° to 85°C.

Bubble control functions are executed by providing current pulses through the appropriate control element on the chip.

1170

The bubble chip is comprised of a gadolinium-gallium garnet substrate upon which a magnetic epitaxial film is grown. Patterns of permalloy metal are deposited on the epitaxial film to define the path of the bubble domains in the presence of a rotating magnetic field. As the field rotates, the bubble domains move under the permalloy pattern in shift register fashion.

The TIB0303 will be offered in a 20-pin dual-in-line package, measuring  $30 \times 30 \times 10$ mm. The package contains the quarter-million-bit bubble chip surrounded by two orthogonal coils that provide the rotating magnetic field, a permanent magnet set, and a magnetic shield to protect data from external fields.

Taking a systems approach, TI will offer a family of interface and control circuits for the TIB0303 in the second quarter of 1979.

### **BLINKING GOOD**

F ONE of your projects requires an l.e.d. to wink on-and-off to catch someone's eye, here's something to save you the effort of building a multivibrator to do it.

Available from the Norbain Optoelectronics Division is the first Flashing Light Emitting Diode, Type FRL 4403, to appear on the market. The T  $1\frac{3}{4}$  l.e.d. is manufactured in Gallium Arsenide Phosphide technology with a red diffused plastic lens. The built-in integrated circuit flashes the l.e.d. on and off at roughly 3 pulses per second, and can be driven directly by standard TTL and CMOS devices, eliminating the need for external switching circuitry.

Optoelectronic characteristics include a luminous intensity of 1.2mCd (typ), an emission peak wavelength of 650nm, spectral line half width 40nm, operating voltage 5 volts (typ), and current of 20 milliamps (typ).

The l.e.d. gives a large full flood radiating area, wide viewing angle and finds application as a condition warning light, monitoring process control system and in many other applications where warning of failure is essential.

Norbain Optoelectronics Division, Norbain House, Arkwright Road, Reading, Berkshire RG2 0LT.

### ON THE LEVELL

THE very popular and stout a.c. microvolt meters, type TM3B, made by Levell Electronics Ltd., have just been upgraded.

The improvements include increased input impedance and meter scale length. A brief specification follows:

VOLTAGE and dB RANGES:  $15\mu V$  to 500V, f.s.d. Acc.  $\pm 1\%$  f.s.d.  $\pm 1\mu V$  at 1kHz, -100,  $-90\ldots +50$ dB. Scale -20dB/+6dB ref. 1mW/600 $\Omega$ .

. RESPONSE:  $\pm 3dB$  from 1Hz to 3MHz,  $\pm 0.3dB$  from 4Hz to 1MHz above  $500\mu V$ .

INPUT IMPEDANCE: Above 50mV:  $10M\Omega < 20$ pf. On  $50\mu V$  to 50mV:  $>5M\Omega < 50$ pf.